SANTA CLARA, Calif.--(

- Magma Software Cost Calculator

- Magma Software Cost Of Computer

- Magma Software Casting

- Magma Software Cost List

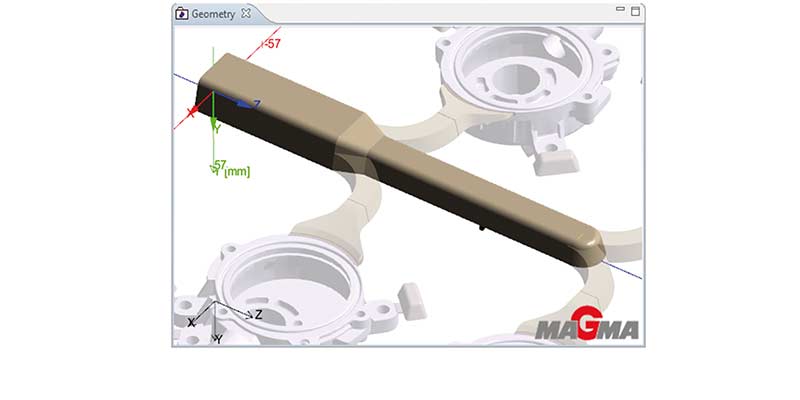

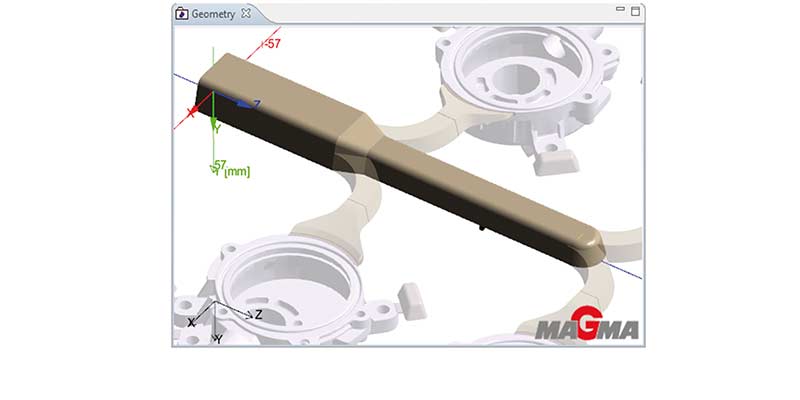

MAGMASOFT is a comprehensive simulation tool for the technological and quality focused production of castings worldwide. Our simulation capabilities show you the way by providing a better understanding of mold filling, solidification, mechanical properties, thermal stresses and distortions, and much more. Worldwide, MAGMA employs more than 230 people in development, support, sales and training, of which 110 are located in Aachen, Germany. 50 software developers, and more foundry engineers than in most foundries, build one of the industry’s most powerful “casting competence centers”. 1x Magma EB3T SAS/SATA Drive Cage For Upto Four 2.5' Drives - LN73344 The portability of the ultra versatile ExpressBox 3T with (4) 2.5” drive bays. The ExpressBox 3T-DB is the ultimate package of expansion and storage for any computing environment.

| New Design Platform Eliminates Need for Manual Floorplanning and Point Tools for Power and Post-Design DFM Processing -- Dramatically Reduces Development Cycle and Design Costs, Speeds Yield Ramp-Up |

Kingdoms of amalur reckoning teeth of naros crack download. Magma(R) Design Automation Inc. (Nasdaq:LAVA), a provider of semiconductor design software, today unveiled Talus(TM), an all-new integrated circuit (IC) implementation product line that offers unequaled automation and virtually unlimited capacity while delivering improved timing, area, power, signal integrity and manufacturability. With Talus, Magma fulfills the promise of electronic design automation (EDA), rather than providing mere electronic design assistance, as traditional tools have. The advanced implementation capabilities in Talus are designed to dramatically reduce the design development cycle and design costs, and speed yield ramp-up for ICs targeted at 65-nanometer (nm) and smaller process geometries.

'Talus delivers what EDA has long promised,' said Rajeev Madhavan, CEO of Magma. 'At each process node, development costs are increasing and profits per design are decreasing. To reverse that trend, IC vendors need true design automation so they can accelerate the design cycle and maximize their engineering resources -- that's what Talus delivers.'

Talus -- Changing the Fundamentals of Chip Design

Talus provides a complete RTL-to-tape-out platform that concurrently analyzes and optimizes timing, area, power, signal integrity and yield. It enables Automated Chip Creation(TM), a new methodology for IC implementation that drastically improves engineering productivity. With Talus, floorplanning has been transformed into an automated physical synthesis process. Leveraging a new constraint set called Relative Placement Constraints(TM), Talus eliminates the need for the traditionally labor-intensive and time-consuming floorplanning and prototyping tasks. Design for variability on complex designs is supported through concurrent multi-mode/multi-corner and native on-chip variation (OCV) analysis with timing and crosstalk noise optimizations. Talus' advanced timing capabilities eliminate the need for iterative analysis and optimization runs to meet multiple mode and corner constraints. Talus also incorporates sophisticated routing algorithms developed in conjunction with IBM and the University of Bonn. Talus is the first system in which the entire implementation flow is lithography-aware. This unique capability minimizes the key source of deterministic variability in 65- and 45-nm designs.

Talus' Automated Chip Creation methodology enables designers to create either preliminary or final-quality layouts, physically flat or hierarchically, in just a few hours and for any size design. The process can begin with as little as 10 percent of the design RTL available. With fast and accurate feedback early in the cycle, users can identify the top-level timing constraints that meet block timing budgets, enabling them to avoid timing violations later during chip integration. With each subsequent RTL change, Talus automatically creates multiple floorplans, allowing designers to see in real-time the impact of those changes on chip size. 2018 sourceoffsite client 5 2 0 for mac.

Predictability for subsequent trials is managed with the Relative Placement Constraints, which enable the user to reproduce desired aspects of a previous floorplan. This unprecedented level of automation expands the user's efficiency at all stages of design development. Early in the process, fast implementation trials can be conducted to establish accurate timing constraints, investigate floorplan alternatives, and trade off package decisions with respect to design speed, area, noise, yield, and power integrity. Sony dcrhc18e drivers for mac. Late in the process, the schedule impact of late-arriving RTL and design requirement changes is minimized because the required production floorplan changes are handled automatically.

Magma Software Cost Calculator

To further accelerate the design cycle and provide the highest capacity, Talus leverages multithreading and distributed processing, allowing users to implement very large designs in just two days. With faster design cycles, higher capacity and the ability to automatically and effectively address all design objectives, Talus users will be able to devote more time to product innovation, reduce IC development costs and increase yields.

Beta Results Demonstrate High QoR and Overnight Runs

A number of full-chip designs targeted for various applications and ranging in size from 4 to 15 million gates have been taken through the Talus flow. Results have demonstrated productivity improvements and significant area savings over conventional design techniques. Heizer solutions manual.

'Hierarchical design demands a significant amount of time and number of resources, especially when the RTL code is changing,' said John Fallin, executive director, Custom SOC Engineering, NEC Electronics America, Inc. 'By using Talus, we will have a viable flat design methodology for 12-million-gate and larger chips that is able to confirm new floorplans overnight, quickly validate chip-level timing constraints, and give us confidence that the design is production worthy.'

Cheat engine company of heroes 2. About Talus Products

The Talus LX and Talus PX products provide the foundation of the Automated Chip Creation methodology for logic and physical design engineers. Both are built on Magma's unified data model architecture offering a tightly integrated IC implementation flow. Talus LX synthesizes chip RTL for given timing, power and placement constraints and automatically generates physical partitions and power and clock prototypes. This automated solution empowers logic designers to rapidly explore the design space and implement the most optimal solution without detailed knowledge of physical design and without sacrificing the schedule, or quality of the design. Talus PX provides complete physical implementation of the design including near abutment layout, final physical partitions, power and signal routing, and chip-level clock tree synthesis. This integrated physical design environment delivers improved timing and signal integrity, smaller area, lower power, better manufacturability, faster turnaround time and higher capacity than conventional point-tool flows.

Both products are currently in limited release. Pricing will be available with the production release scheduled for 2006.

About Magma

Magma's software for integrated circuit (IC) design is recognized as embodying the best in semiconductor technology. The world's top chip companies use Magma's EDA software to design and verify complex, high-performance ICs for communications, computing, consumer electronics and networking applications, while at the same time reducing design time and costs. Magma provides software for IC implementation, analysis, physical verification, characterization and programmable logic design, and the company's integrated RTL-to-GDSII design flow offers 'The Fastest Path from RTL to Silicon'(TM). Magma is headquartered in Santa Clara, Calif. with offices around the world. Magma's stock trades on Nasdaq under the ticker symbol LAVA. Visit Magma Design Automation on the Web at www.magma-da.com.

Magma is a registered trademark, and Automated Chip Creation, Relative Placement Constraints, Talus and 'The Fastest Path from RTL to Silicon' are trademarks of Magma Design Automation Inc. All other product and company names are trademarks or registered trademarks of their respective companies.

Magma Software Cost Of Computer

Pokemon sun rom for citra for mac. Forward-Looking Statements:

Magma Software Casting

Magma Software Cost List

Except for the historical information contained herein, the matters set forth in this press release, including statements that: Magma software offers unequaled automation and unlimited capacity; delivers improved timing, area, power, signal integrity and manufacturability; reduces the development cycle and costs and speeds yield ramp-up; and will be in production release in the summer of 2006 are forward-looking statements within the meaning of the 'safe harbor' provisions of the Private Securities Litigation Reform Act of 1995. These forward-looking statements are subject to risks and uncertainties that could cause actual results to differ materially including, but not limited to Magma's ability to keep pace with rapidly changing technology and the company's products' abilities to produce desired results. Further discussion of these and other potential risk factors may be found in Magma's public filings with the Securities and Exchange Commission (www.sec.gov). Magma undertakes no additional obligation to update these forward-looking statements.